International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

Vol. 9, Issue 5, May 2021

DOI 10.17148/IJIREEICE.2021.9524

# ASYMMETRICAL MULTILEVEL INVERTER WITH ADVANCED PWM TECHNIQUES

Sangeeta Ahirwar

Student, Dept. of Electrical Engineering, MITS Gwalior, M.P., India

**Abstract** – In this paper a "Asymmetric Multilevel inverter with advanced PWM techniques" is proposed Proposed MLI includes single source, less range of switches, diodes, and capacitors, total harmonic distribution, harmonic spectrum. As such per simulation result as we increase the voltage level of inverter, the harmonic will reduced. Implementation of Asymmetrical Multileve<u>I</u> with advanced PWM techniques by using MATLAB/SIMULINK.

Key words: MLI Simulation, PDPWM, PODWM, APODPWM method, THD.

# **I**.INTRODUCTION

Multilevel Converters are finding increased attention in industry and academia as one of the preferred choices of electronic power conversion for high power applications. They have successfully made their way into the industry and therefore considered as a mature and proven technology. The concept of multilevel converters has been introduced since 1975. The cascaded multilevel inverter was first proposed in 1975. The term multilevel begin with three-level converter. In 1981, diode clamped multilevel inverter also called neutral point clamped (NPC) inverter schemes were proposed. In 1982, capacitor clamped (flying capacitor) and in 1996

## **II. PROPOSED TOPOLOGY**

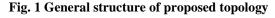

This dissertation presents a new topology based on asymmetrical multilevel inverter. This proposed topology has reduced number of switches and lower harmonic distortion in the output voltage in comparison to conventional multilevel inverter topology. It consists of two voltage source ( $V_1$  and  $V_2$ ) with different magnitude and six unidirectional switches (S1, S2, S3, S4, S5, S6.)

# 1. Operation of a Proposed 7 Level Asymmetrical MLI Topology

producing 7 levels in output voltage, proposed topology required two voltage source ( $V_1$  and  $V_2$ ) with different magnitude and six

unidirectional switches  $(S_1, S_2, S_3, S_4, S_5, and S_6)$ . For generating all positive and negative levels, magnitude of voltage sources  $(V_1 : V_2)$  should be in the ratio (1 : 2). it is clear that the switching combinations  $(S_1, S_2)$ ,  $(S_3, S_4)$ , and  $(S_5, S_6)$  should not be turned 'ON' simultaneously.

# TABLE 1. Switching Scheme of Proposed Asymmetrical MLI

| State | Switching Scheme |     |     |     |     |     | Output      |

|-------|------------------|-----|-----|-----|-----|-----|-------------|

|       | Sı               | S2  | Si  | S4  | S5  | Sí  | Voltage     |

| 1     | ON               | OFF | OFF | ON  | ON  | OFF | $V_2 + V_1$ |

| 2     | ON               | OFF | OFF | ON  | OFF | ON  | V2          |

| 3     | OFF              | ON  | OFF | ON  | ON  | OFF | Vı          |

| 4     | OFF              | ON  | OFF | ON  | OFF | ON  | 0           |

| 5     | ON               | OFF | ON  | OFF | OFF | ON  | -V1         |

| 6     | OFF              | ON  | ON  | OFF | ON  | OFF | -V2         |

| 7     | OFF              | ON  | ON  | OFF | OFF | ON  | -(V2 + V1)  |

**Copyright to IJIREEICE**

International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

Vol. 9, Issue 5, May 2021

## DOI 10.17148/IJIREEICE.2021.9524

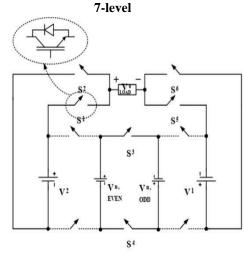

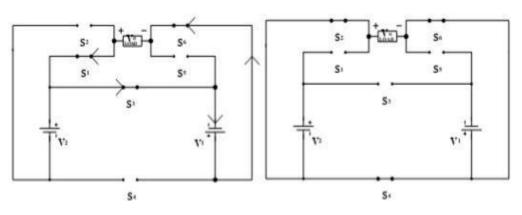

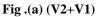

# 2. Operating Modes of Proposed 7-level Asymmetrical MLI

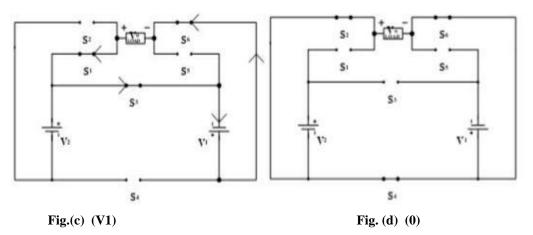

# Fig. 2 (a-g) are the different operating modes of ASMLI

Fig. (b) (V2)

International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

Vol. 9, Issue 5, May 2021

#### DOI 10.17148/IJIREEICE.2021.9524

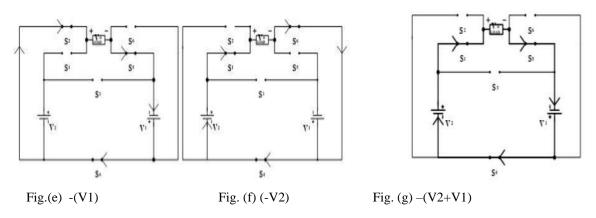

#### III. .SIMULATION OF PROPOSED 7-LEVEL ASMLI TOPOLOGY

Proposed 7-Level MLI is simulated with the help of MATLAB/Simulink R2013a software version. The simulation parameters for 7-Level MLI are as follows: Resistance R=10  $\Omega$ , and DC Voltage sources are V<sub>1</sub>=50V & V<sub>2</sub>=100V.Frequency of carrier signal is 2 kHz and Frequency of Reference signal is 50 Hz. For harmonics calculations, Frequency Modulation (M<sub>f</sub>) is 40, and Modulation Index (M<sub>a</sub>) is variable.

Fig. 3 Model of single- Phase 7-Level Asymmetrical MLI

## **IV. SIMULATION RESULTS**

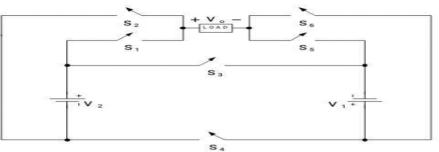

Fig.4 shows the output phase voltage result of a 7-level MLI with PODPWM technique. Table 2 represents THD at different modulation index. For 7- level MLI, corresponding THD in % are shown in Fig.

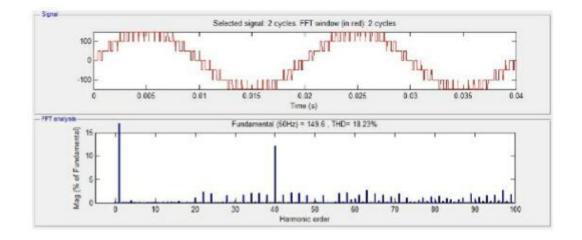

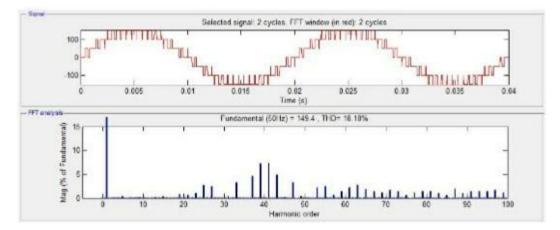

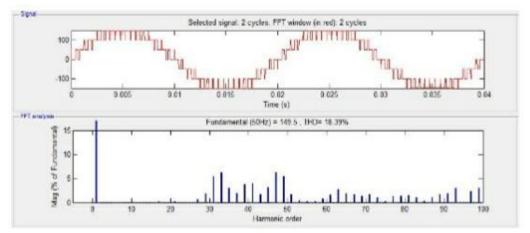

**Fig.4. Output Voltage Waveform of Proposed 7-Level Asymmetrical MLI** Comparative analysis of THD for different PWM techniques . For 7-level MLI, corresponding Total Harmonic distortion in % (% THD) PD= 18.23, POD= 18.18, APOD=18.39 at modulation index (Ma) = 1.0

**Copyright to IJIREEICE**

International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

Vol. 9, Issue 5, May 2021

#### DOI 10.17148/IJIREEICE.2021.9524

Fig 5.THD of 7-Level ASMLI PDPWM for R-Load (Ma=1.0&Mf=40)

Fig. 6. THD of 7-Leve ASMLI PODPWM for R-Load (Ma =1.0&Mf=40)

Fig.7.THD of 7-Leve ASMLI APODPWM for R-load (Ma=1.0&Mf=40)

**Copyright to IJIREEICE**

International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

Vol. 9, Issue 5, May 2021

#### DOI 10.17148/IJIREEICE.2021.9524

## TABLE- 2. Comparative THD analysis of different PWM techniques for 7-level ASML6. V. CONCLUSION

| Modulation<br>Index | PDPWM | PODPWM | APODPWM |  |

|---------------------|-------|--------|---------|--|

| 1                   | 18.23 | 18.18  | 18.39   |  |

| 0.95                | 20.59 | 20.60  | 20.23   |  |

| 0.90                | 22.40 | 22.11  | 21.98   |  |

| 0.85                | 23.62 | 23.49  | 23.25   |  |

| 0.80                | 24.30 | 24.07  | 24.19   |  |

The Asymmetrical proposed topology for 7-level MLI are implemented. For 7-level the % THD result is shown in Table 2 respectively with different PWM techniques and modulation indices. From these results it can be concluded that with the increase of number of level of output near sine wave is obtained which offers less THD and less distortion. The simulation results for 7- level with asymmetrical MLI topology are presented in this . The value of harmonic distortion have been calculated at different modulation index and PWM techniques.

#### ACKNOWLEDGEMENT

I would like to express my gratitude to my professor, who guided me throughout this paper. I wish to acknowledge by the help provided by the technical. I would like to show my appreciation. I offer my sincere appreciation for the learning opportunities provided by my mentor.

#### REFERENCES

[1] R.H. Baker, "High-voltage converter circuits", U.S. patent Number 4, 203, 151, 1980.

[2] J. Rodriguez, J-S. Lai, and F. Z. Peng, "Multilevel inverters: A survey of Topologies, controls and applications", IEEE Trans. Ind. Electron., Vol.49, pp.724-738, 2002.

[3] L. M. Tolbert, F. Z. Peng, and T. Habetler, "Multilevel converters for Large Electrical drives", IEEE Trans. Ind. Applocant., vol.35, pp. 36-44, 1999

[4] J. Rodriguez, S. Bernet, B. Wu, J. Pontt, and S. Kouro, "Multilevel voltage- Source converter topologies for Industrial medium-voltage drives", IEEE. Trans. Ind. Electron, vol.54, pp.2930- 2945,2007.

[5] S. Mariethoz and A. Rufer, "New configurations for the three phase asymmetrical multilevel inverter", in conf. Rec. IEEE IAS Annual Meeting, vol.2, pp. 828-835, 2004.

[6] S. Daher, J. Schmind, and F.L.M. Artunes, "Multilevel Inverter Topology for Stand-Alone PV Systems", IEEE. Trans. Ind. Electron, vol.55, pp.2703-2712, 2008.

[7] A. Radan, A.H. Shahirinia, and M. Falahi, "Evolution of carrier based PWM methods for multi-level inverters", in Proc. IEEE ISIE, pp.389-394, 2007.

[8] X.Yuan and I.Barbi, "Fundamentals of a New Diode Clamping Multilevel Inverters", IEEE. Transaction Power Electro., vvol.15, pp.389-394, 2007.