International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

Vol. 8, Issue 7, July 2020

# Optimized ALU with BIST Implementation using Encounter Platform

#### Karthik N S<sup>1</sup>, Srinath M S<sup>2</sup>

Senior VLSI Engineer, E&C, PES College of Engineering, Bangalore, India<sup>1</sup>

Assistant Professor, EEE, PES College of engineering, Bangalore, India<sup>2</sup>

**Abstract:** This paper provides an Optimized Arithmetic Logical Unit (ALU) with BIST capability, ALU comprising of different arithmetic operations and logical operations is implemented. ALU is used in many processing and computing devices, due to rapid development of technology not only the faster arithmetic unit is required but also less area and low power arithmetic units are needed and due to the increasing integration complexities of IC's the Optimized ALU implemented sometimes may malfunction, so testing capability must be provided and this is accomplished by Built In Self-Test (BIST) for Optimized ALU. In this project the implementation will be done in Encounter platform.

Keywords: ALU, BIST, Vedic Algorithm, Cadence Encounter, Xilinx.

#### I. INTRODUCTION

Arithmetic Logic Unit (ALU) is an important and necessary unit present in every processor and all computing devices performing arithmetic operations like addition, subtraction, multiplication, increment, decrement, shifting and logical operations like and, or, not, exor. The ALU must be optimized and when manufactured they might have defects or might be faulty hence to increase testability Design for Testability (DFT) must be provided one such methodology is Built-In-Self Test (BIST). BIST technique provides little cost, a well-defined increase in the testability of the Circuit Under Test (CUT). The test pattern generator is a part of BIST implemented using Linear feedback Shift Register (LFSR), this increases the testability of ALU.

#### II. PROPOSED METHOD AND IMPLEMENTATION

Optimized ALU implementation for increasing speed and decreasing power and delay, fast adder like Carry Save Adder is implemented and fast multiplier like Vedic multiplier one of the vedic techniques is implemented, by using particular adder and multiplier units area, power and delay optimization is achieved in ALU. BIST uses test pattern generators to generate test patterns then these test patterns are applied to circuit under test that is ALU and the output is analysed and the functionality is tested.

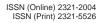

Fig1:ALU Architecture

Using carry save addition, the delay can be reduced. The methodology is to take 3 numbers that we want to add together, x + y + z, and convert it into two numbers c + s such that x + y + z = c + s, will be computed in short time. In carry save addition, we directly pass carry to final step.

## International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

| Vol. 8, Issue 7, July 2020 |                                  |           |              |       |                         |      |

|----------------------------|----------------------------------|-----------|--------------|-------|-------------------------|------|

| X: 1                       | 0011                             | X: 1      | 0011         | X:    | 10011                   |      |

| Y: + 1                     | 1001                             | Y: + 1    | 1001         | Y:    | + 1 1 0 0 1             |      |

| Z: + (                     | 01011                            | Z: + 0    | 1011         | Z:    | +01011                  |      |

| S: 0                       | 0 0 0 1                          | C: 11     | 011          | S:    | 00001                   |      |

|                            |                                  |           |              | C:    | 11011                   |      |

|                            |                                  |           |              | Sum:  | 110111                  |      |

| Fig2:CSA addition          |                                  |           |              |       |                         |      |

|                            |                                  | -         |              |       |                         |      |

| A0 B0 C0                   | A1 B1                            | <u>C1</u> | A2 B2        | 2 C2  | A31 B31 C31             |      |

|                            |                                  |           |              |       |                         |      |

|                            |                                  |           |              |       |                         |      |

| FA1                        | FA2                              |           | FA3          | 3     | FA8                     |      |

|                            |                                  |           |              |       |                         |      |

| $\downarrow \downarrow$    | $\downarrow\downarrow\downarrow$ |           | $\downarrow$ | /     | $\downarrow \downarrow$ |      |

| S0 C0                      | S1 C1                            |           | S2 (         | C2    | S31 C31                 |      |

| S0 C0                      | <u>S1</u>                        | C1        | S2           | C2    | S31 C31                 |      |

|                            |                                  |           |              |       |                         |      |

|                            |                                  |           |              |       |                         | cout |

| FA1                        | → FA2                            |           | → FA3        | }     | FA8                     |      |

|                            |                                  |           |              |       |                         |      |

| Fig3:CSA Architecture      |                                  |           |              |       |                         |      |

|                            |                                  |           |              |       | _                       |      |

|                            | Sl.No Add                        |           | ler          | Delay | _                       |      |

|                            |                                  | _         |              |       |                         |      |

|                            | 1                                | CL.       | A            | 648ps |                         |      |

|                            | 2                                | CS.       | A            | 144ps |                         |      |

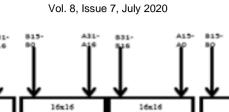

Subtraction: The 2's Complement Addition technique is used for subtraction, as adder block is optimised using carry save adder ,subtraction unit is also optimised.Multiplier unit is optimized using Vedic Multiplier technique this increases

Fig4: Comparision of adders

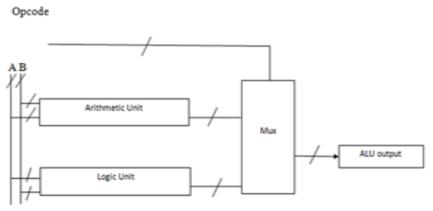

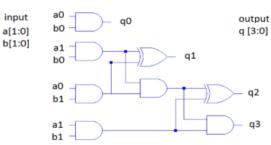

**2x2 Multiply Block** Fig5:Mutiplier Representation

speed and decreases power.

### **IJIREEICE**

## International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

Fig6:2×2 Multiplier hardware representation

Fig 1. A 2x2 Vedic multiplier

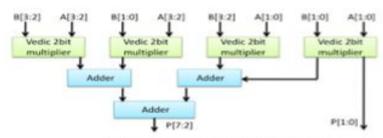

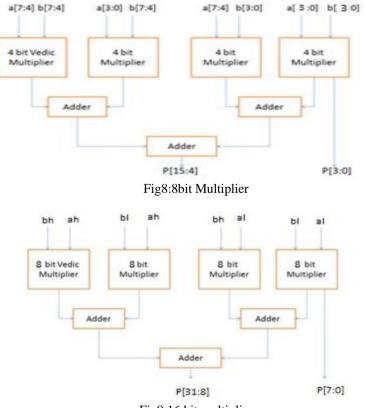

#### 4-bit Vedic multiplier using 2-bit multipliers Fig7:4 bit multiplier

Fig9:16 bit multiplier

.....

### International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

Optimized ALU

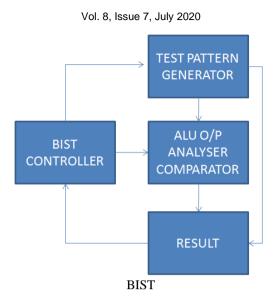

After designing and implementing Optimized ALU, BIST has to be implemented, the diagram of BIST is as shown in the diagram, it has BIST controller which selects whether it should work either in testing mode or normal mode, it has test pattern generators like LFSR linear feedback shift register which generates test patterns these test patterns are applied to circuit under test that is optimized ALU over here then the result obtained is analysed and checked for correctness of ALU. LFSR is an n-bit shift register which randomly produces test vectors till 2n-1 very quickly due to minimum usage of combinational.

logic. The usage of exclusive-OR gates and shift register produces binary sequence at each flip-flop. By proper selection of points at which we take the feedback from an n-bit shift register we can produce a PRBS of length 2n - 1, that includes all possible patterns of n bits, in which all-zeros pattern is excluded. In an LFSR, the bits at selected positions of shift register are fed back into the register's input bit.

### IJIREEICE

#### International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

III. CONCLUSION

In this paper we have implemented Optimized ALU with BIST capability which has lesser area, power and delay implemented using carry save adder and vedic multiplier with testing capability provided by Built in Self Test provides testing capability.

#### REFERENCES

- [1] Veeramachaneni, S.; Srinivas, M.B., "Design of optimized arithmetic circuits for multiplier realization," *Microelectronics and Electronics* (*PrimeAsia*), 2013 IEEE Asia Pacific Conference on Postgraduate Research in, vol., no., pp.219,224, 19-21 Dec. 2013

- [2] Saha, S.; Rahman, M.A.; Thakur, A., "Design and implementation of a BIST embedded high speed RS-422 utilized UART over FPGA," Computing, Communications and Networking Technologies (ICCCNT),2013 Fourth International Conference on, vol., no., pp.1,5, 4-6 July 2013

- [3] Gurjar, P.; Solanki, R.; Kansliwal, P.; Vucha, M., "VLSI implementation of adders for high speed ALU," India Conference (INDICON), 2011 Annual IEEE, vol., no., pp.1,6, 16-18 Dec. 2011

- [4] Voyiatzis, I., "An ALU-Based BIST Scheme for Word-Organized RAMs," Computers, IEEE Transactions on , vol.57, no.5, pp.577,590, May 2008 [5] Seongmoon Wang, "A BIST TPG for Low Power Dissipation and High Fault Coverage," Very Large Scale Integration (VLSI) Systems, IEEE Transactions on , vol.15, no.7, pp.777,789, July2007

- [6] Le Blanc, C.; Colinet, E.; Juillard, J.; Anghel, L., "Digital Implementation of a BIST Method based on Binary Observations," *Digital System Design Architectures, Methods and Tools, 2008. DSD '08. 11th EUROMICRO Conference on*, vol., no., pp.709,713, 3-5 Sept. 2008

- [7] Bartlett, V.A.; Dempster, A.G., "Using carry-save adders in low-power multiplier blocks," *Circuits and Systems, 2001. ISCAS 2001. The 2001 IEEE International Symposium on*, vol.4, no., pp.222,225 vol. 4, 6-9 May 2001

#### BIOGRAPHY

Karthik NS is Senior VLSI Engineer worked for Various Tire 1 VLSI Product Organizations

Srinath M S is Assistant Professor working at PES College of Engineering