International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

Vol. 7, Issue 3, March 2019

# Performance Analysis of Fully-Depleted Silicon-On-Insulator (SOI) G<sup>4</sup>-FET and Gate-All-Around (GAA) MOSFETs

### Md. Rakibul Alam<sup>1</sup>, Md. Rais Uddin Mollah<sup>2</sup>, Md. Ferdous Khan<sup>3</sup>

Lecturer, Department of Electrical and Electronic Engineering, Sonargaon University, Dhaka, Bangladesh<sup>1,2,3</sup>

**Abstract:** The performance of fully-depleted Silicon-On-Insulator (SOI) Four Gate Transistor ( $G^4$ -FET) and Gate-All-Around (GAA) MOSFETs are investigated. Threshold voltage, Subthreshold Swing (SS), Drain Induced Barrier Lowering (DIBL), maximum drain current are calculated and compared.

**Keywords:** Silicon-on-Insulator (SOI), Four Gate Transistor ( $G^4$ -FET), Gate-All-Around (GAA), Subthreshold Swing (SS), Drain Induced Barrier Lowering (DIBL)

### I. INTRODUCTION

The continuous scaling of GAA silicon nanowire Field Effect Transistor (FET) [1], [2] illustrates better control of short channel effect over other structures [3] due to their gate controllability, low leakage, high on-off ratio and carrier transport property [4]. For better SS and DIBL, channel length, channel width, channel height, oxide thickness can be considered as important design parameters [5], [6]. The  $G^4$ -FET which is a double gate MOSFET consisting of two lateral junction-gates and it has a lateral double-gate MOS consisting of two vertical MOS gates (top-gate and bottom-gate). In GAA MOSFETs, the gate oxide and the gate electrodes wrap around the channel region.  $G^4$ -FET and GAA MOSFETs based circuits are feasible with a fully-depleted SOI process without requiring any additional fabrication steps. Drain current flows through the channel and the conducting channel surrounded by the depletion regions. In this paper, threshold voltage, SS, DIBL, maximum drain current of  $G^4$ -FET and GAA MOSFETs are calculated and compared.

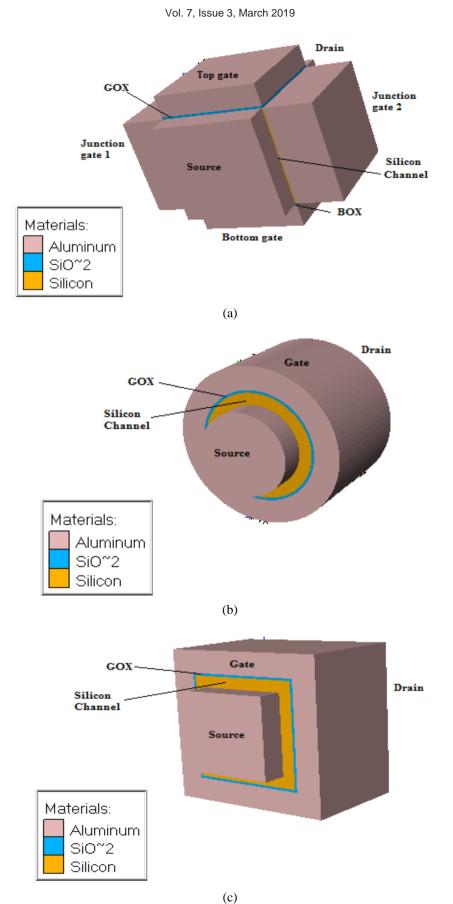

### II. G<sup>4</sup>-FET AND GAA MOSFETS DEVICE STRUCTURE AND SIMULATION

In this work, we demonstrate the 90-nm fully depleted SOI  $G^4$ -FET and GAA MOSFETs structures. Device simulations were performed by 3D SILVACO/ATLAS simulator. Device parameters of  $G^4$ -FET and GAA MOSFETs are given below:

| Device parameters                | G⁴-FET                             | Cylindrical GAA MOSFET             | Cubical GAA MOSFET                 |

|----------------------------------|------------------------------------|------------------------------------|------------------------------------|

| Channel length                   | 90 nm                              | 90 nm                              | 90 nm                              |

| Channel width/ Channel           | 90 nm                              | 90 nm                              | 90 nm                              |

| diameter                         |                                    |                                    |                                    |

| Channel height                   | 90 nm                              | -                                  | 90 nm                              |

| Gate oxide thickness/            | 2 nm                               | 2 nm                               | 2 nm                               |

| surrounding gate oxide thickness |                                    |                                    |                                    |

| <b>Buried oxide thickness</b>    | 2 nm                               | -                                  | -                                  |

| Top gate thickness/ surrounding  | 20 nm                              | 20 nm                              | 20 nm                              |

| gate thickness                   |                                    |                                    |                                    |

| Bottom gate thickness            | 20 nm                              | -                                  | -                                  |

| Junction gates width             | 40 nm                              | -                                  | -                                  |

| Doping density of junction gates | $1 \times 10^{20} \text{ cm}^{-3}$ | -                                  | -                                  |

| ( <b>p</b> <sup>+</sup> )        |                                    |                                    |                                    |

| Channel doping density (n)       | $1 \times 10^{17} \text{ cm}^{-3}$ | $1 \times 10^{17} \text{ cm}^{-3}$ | $1 \times 10^{17} \text{ cm}^{-3}$ |

| doping density of drain and      | $1 \times 10^{20} \text{ cm}^{-3}$ | $1 \times 10^{20} \text{ cm}^{-3}$ | $1 \times 10^{20} \text{ cm}^{-3}$ |

| source (n <sup>+</sup> )         |                                    |                                    |                                    |

Table I Device Parameters of G<sup>4</sup>-FET and GAA MOSFETS

### **IJIREEICE**

## International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

### **IJIREEICE**

## International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

Vol. 7, Issue 3, March 2019

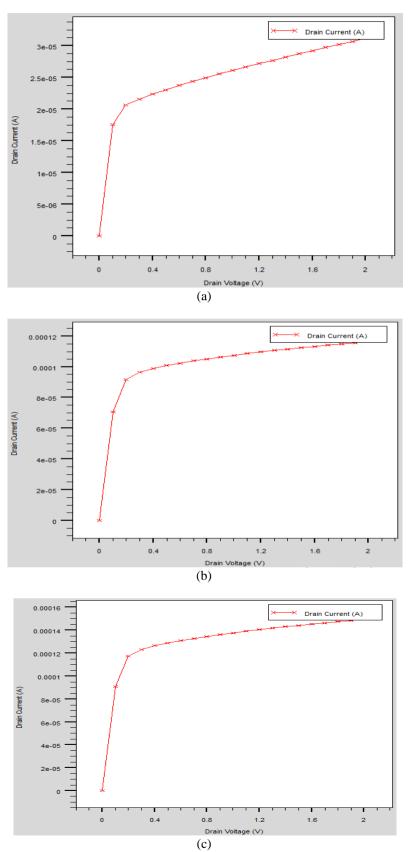

Fig. 2 Current-Voltage characteristics at Vg= 0.2 V of (a) G<sup>4</sup>-FET, (b) Cylindrical GAA MOSFET, (c) Cubical GAA MOSFET

## International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

Vol. 7, Issue 3, March 2019

### III. RESULTS AND DISCUSSIONS

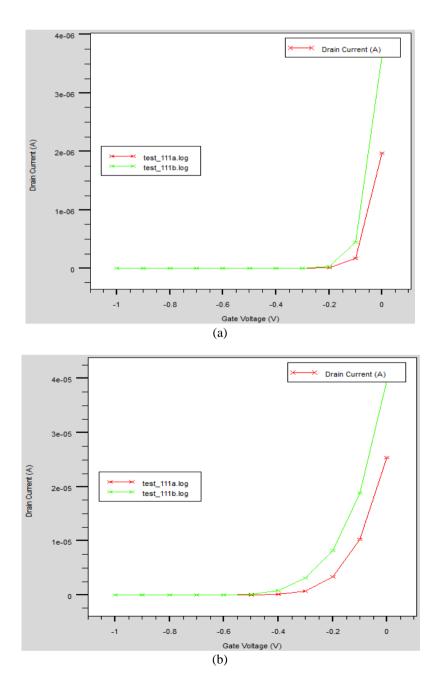

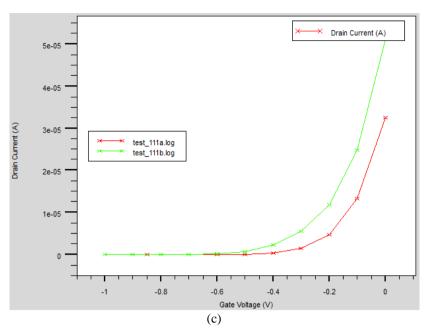

Fig. 2 shows the current-voltage characteristics of  $G^4$ -FET and GAA MOSFETs. Maximum drain current of cubical GAA MOSFET is larger than other two structures (Table II). DIBL was calculated as the difference in threshold voltage when the drain voltage was increased from 0.1 to 0.8 V. Fig. 3 shows the transfer characteristics of  $G^4$ -FET and GAA MOSFETs. Threshold voltage of cubical GAA MOSFET is smaller than other two structures. But SS and DIBL of  $G^4$ -FET are smaller than other two structures.

| Properties       | G <sup>4</sup> -FET | Cylindrical GAA MOSFET | Cubical GAA MOSFET |

|------------------|---------------------|------------------------|--------------------|

| V <sub>TH</sub>  | -0.1095 V           | -0.1676 V              | -0.1682 V          |

| SS               | 77.93 mV/dec        | 89.04 mV/dec           | 98.48 mV/dec       |

| DIBL             | 6.66 mV/V           | 32.56 mV/V             | 37.02 mV/V         |

| I <sub>max</sub> | 31.17 µA            | 116.4 µA               | 149.56 μA          |

### IJIREEICE

#### International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

Vol. 7, Issue 3, March 2019

Fig. 3 Transfer characteristics of (a) G<sup>4</sup>-FET, (b) Cylindrical GAA MOSFET, (c) Cubical GAA MOSFET

### CONCLUSION

We compared SOI  $G^4$ -FET and GAA MOSFETs through 3D SILVACO/ATLAS simulator. Threshold voltage, SS, DIBL, maximum drain current are calculated and compared. In the future these devices can be used in the fast switching circuits.

#### ACKNOWLEDGMENT

The authors acknowledge the contribution of the Department of Electrical and Electronic Engineering, Sonargaon University (SU) for the permission to use computing facilities.

#### REFERENCES

- P.Gulati and Mrs. M.Gupta, "Design and Characteristic Analysis of Gate All Around Nanowire MOSFET and Its Application", IJIR, Vol. 3, Issue-7, pp. 752-765, 2017.

- [2] T. Wang, L. Lou and C. Lee, "A Junctionless Gate-All-Around Silicon Nanowire FET of High Linearity and Its Potential Applications", IEEE Electron Device Lett., Vol. 34, no. 4, pp. 478-480, 2013.

- [3] S. Bangsaruntip, G. M. Cohen, A. Majumdar and J. W. Sleight, "Universality of Short-Chennel Effects in Undoped-Body Silicon Nanowire MOSFETs", IEEE Electron Device Lett., Vol. 31, no. 9, pp. 903-905, 2010.

- [4] A. Sharmaand S. Akashe, "Performance Analysis of Gate-All-Around Field Effect Transistor for CMOS Nanoscale Devices", International Journal of Computer Applications, Vol. 84, no. 10, pp. 44-48, 2013.

- [5] Y.-K. Choi, N. Lindert, P. Xuan, S. Tang, D. Ha, E. Anderson, T.-J. King, J. Bokor, and C. Hu, "Sub-20 nm CMOS FinFET technologies," in Tech. Dig. IEDM, pp. 421–424, 2001.

- [6] B. S. Doyle, S. Datta, M. Doczy, S. Hareland, B. Jin, J. Kavalieros, T. Linton, A. Murthy, R. Rios, and R. Chau, "High performance fullydepleted tri-gate CMOS transistors," *IEEE Electron Device Lett.*, vol. 24, no. 4, pp. 263–265, 2003.