National Conference on Advanced Innovation in Engineering and Technology (NCAIET-2015)

Alva's Institute of Engineering and Technology, Moodbidri

Vol. 3, Special Issue 1, April 2015

# High Speed IP Based Architecture for Telecommand System on chip (SoC)

## Anupama Muralidharan

M.Tech, Department of ECE, VTU University, MITE Moodbidre, Karnataka

Abstract: An IP (intellectual property) core is a block of logic or data that is used for making a field programmable gate array (FPGA) or application-specific integrated circuit (ASIC) for a product. Design reuse IP cores are part of the growing electronic design automation (EDA) industry which allows the repeated use of previously designed components. Using many IP cores a system itself can be designed, System on Chip (SoC) offers this requirement. In the current telecommand communication method, excess number of physical devices is present, which cause a major communication delay. Combining many of the predesigned internal blocks in to a single chip can solve this problem. The paper is concerned with the design of telecommand and telemetry system and its peripheral devices like combined memory and error detection and correction (EDAC) unit.

Keywords: EDAC, Telecommand, SoC.

#### I. **INTRODUCTION**

The semiconductor industry has continued to make into a pre-arranged format (which may follow a standard impressive improvements in the Very Large-Scale Integrated (VLSI) circuits. In order to keep pace with the levels of integration available, design engineers have developed new methodologies and techniques to manage the increased complexity occurs in these large chips. One such emerging methodology is system-on-chip (SoC) design, wherein predesigned and pre-verified blocks often called intellectual property (IP) blocks, IP cores, or virtual components obtained from internal sources, or third parties, and combined on a single chip. These reusable IP cores may include embedded processors, memory blocks, interface blocks, analog blocks, and components that handle application specific processing functions. Corresponding software components are also provided in a reusable form and may include real-time operating systems and kernels, library functions, and device drivers.

A System on a Chip or System On Chip (SoC or SOC) is an Integrated Circuit (IC) which integrates all the components of a computer or any other electronic system into a single chip. It is a group of all components and it's subcomponents of a system on to a single chip. SoC design allows high performance, miniaturization, good process technology, cost sensitivities and an efficient battery life time. This innovation in design had been used by many designers .Advantages includes the high performance and low power consumption, cost, and size.

A telecommand is a command sent to control remote system or systems i.e. not directly connected (e.g. via wires) to the place from which the telecommand is sent. The telecommand word is derived from tele = remote (Greek), and command = to entrust/order (Latin). Systems that need remote measurement and reporting of information of interest to the system designer or operator, require the counterpart of telecommand, telemetry. For a telecommand (TC) to be effective, it must be compiled

structure), modulated onto a carrier wave which is then transmitted with adequate power to the remote system. The remote system will then demodulates the digital signal from the carrier, decode the telecommand, and execute it. Transmission of the carrier wave can be by ultrasound, infra-red or other electromagnetic. For effective control of the various satellite sub-systems under all conditions, a highly efficient and responsive telecommand (TC) system is absolutely essential. Some of the important operations performed by the telecommand system include energizing various subsystem, tape recorder operations, spin-up of satellite etc. Since remote control through telecommand system is the mainstay for these operations to be reliably performed in the satellite in orbit, the system has to work with a high degree of reliability design wise. Inclusion of many physical devices in the whole communication system always makes communication delays. Combining certain blocks of system can reduce such delays.

#### II. LITERATURE SURVEY

The work titled "designing of telecommand system using SoC for space craft control application"[5], describes the importance of checking the integration between components in the whole system and advantage of using pre-defined and pre-verified IP units in space communication like telecommand system. In the paper "FPGA implementation of SoC architecture for space craft application" introduces the UART (Universal Asynchronous Receiver and Transmitter) to transmit data in to ground station and implementation of entire system in to FPGA, which is a future work of [5].

But the architecture using VIRTEX 5 FPGA device makes a tradeoff between frequency and time delay with 48% increase in operating frequency and having a minimum time delay of about 5%.

National Conference on Advanced Innovation in Engineering and Technology (NCAIET-2015)

Alva's Institute of Engineering and Technology, Moodbidri

## Vol. 3, Special Issue 1, April 2015

The work titled "system on chip: reuse and integration" Number of arrays on a memory chip is determined by deals with the introduction of IP based blocks which are certain parameters. They include the speed at which the reusable in nature. It also describes the possibility of integration of many such units in to a single chip i.e. SoC designs. [7]

#### III. **DESIGN METHODOLOGY**

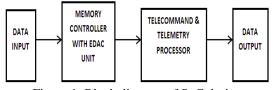

This paper can be implemented as the telecommand System-on-a-Chip (SoC) in the On-Board System (OBS). For that each unit in the entire system treated as IP cores. To build the system on-a-chip, hardware description the byte size. The size of an SRAM with m address lines language VHDL is used. The overall telecommand system is the integration of SRAM, PROCESSOR and EDAC Unit. To overcome the shortfall of the present design B. where the major drawback has been the increased delay and decrease in frequency for transmission of data packets, the new architecture is designed as shown in Figure 1. [20]

Figure 1: Block diagram of SoC design

#### Α. Design of SRAM

Static random-access memory (SRAM) is a type of semiconductor memory. For storing bits in the memory it uses the bistable latching circuitry. SRAM is a volatile memory, means data will loss when the memory is not powered. But still it has significance in terms of speed of access. The other type of memory DRAM (Dynamic RAM) can delete the data as well as refresh while running the program.

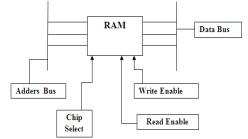

The basic architecture of a static RAM contains 3. rectangular arrays of memory cells with support circuitry. Depending on the data to be stored, cell numbers vary. The support circuitry is used to decode addresses, and to implement the required read and write operations .The block diagram of 2k x 32 bit SRAM is shown in Figure 2.

Figure 2: Block diagram of 2K x32 bit SRAM

SRAM memory arrays are arranged in rows and columns and each section is called a memory cell. The rows are called word lines and the columns are called bit lines. A memory cell is said to be a unique location or address defined by the intersection of a row and column. This intersection is linked to a specific data input/output pin.

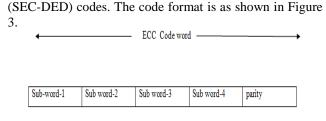

An error-correcting code (ECC) is a system of adding redundant data, or parity data, to a message, such that it can be recovered by a receiver even when a number of errors (up to the capability of the code being used) were introduced, either during the process of transmission, or on storage. The modified Hamming Code is widely used for Single-Error Correctable and Double-Error Detectable

С.

in

memory must operate, total size of the memory, the

number of data inputs and outputs on the chip and layout

and testing requirements. Memory arrays are considered as the vital building block for designing as well as

implementing any digital systems. Memory size is large

for any of the digital system. Physical area takes for the

SRAM can calculated as follows. For an Nxn SRAM array

where 'N' indicates the number of bytes and 'n' indicates

In information theory and coding theory with applications

detection and correction or error control are techniques that enable reliable delivery of digital data over unreliable

communication channels. Many communication channels

are subject to channel noise, and thus errors may be

introduced during transmission from the source to a

receiver. Error detection means to decide whether the received data is correct or not without having a copy of the

original message.Error detection uses the concept of redundancy, which means adding extra bits for detecting

computer science and telecommunication, error

and n data lines is 2/m words, or  $2^n m x n$  bits

Design of EDAC unit

errors at the destination.[1]

Data word Figure 3: ECC code word format

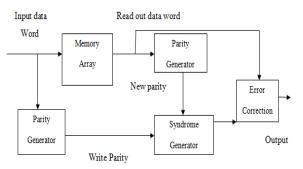

## Integration of SRAM with EDAC unit

A low Earth orbit (LEO) is an orbit around Earth with an altitude between 160 kilometres (99 mi), (orbital period of about 88 minutes), and 2,000 kilometres (1,200 mi) (about 127 minutes). All manned space stations to date, as well as the majority of satellites, have been in LEO. The data stored in LEO are digital in nature. These digital data always have undergone some kind of disturbances. SEUs (single event upset) is the main among them. It is caused by radiations like UV, IR and gamma radiations. This adversely effects memory chips. Error detection and correction techniques are helpful to handle this problem.

National Conference on Advanced Innovation in Engineering and Technology (NCAIET-2015)

Alva's Institute of Engineering and Technology, Moodbidri

## Vol. 3, Special Issue 1, April 2015

For the secure transaction of data between the CPU of the other subsystems of the satellite as shown in fig 6. In PAN on board computer and its local RAM, the program coordinator, received command from the EDAC unit and memory has generally been designed by applying the transfer to the Full Function Devices (FFD's) in Hamming code.

Figure 4: Integration of SRAM with EDAC unit

In the error control the designation (n, k) denotes a block of code that takes a k-bit data word and maps it to an n-bit code word. The importance of reducing the size as well as integration of units is here. There is a chance of occurring two bit error in a single byte. Before the second error comes the first error should clear by the computer. In the Fig.4 the Parity Generator generates the parity from the input data word. The entire code word, which includes the data word and parity word, is written into the memory when it performs the WRITE operation. In a READ operation, the data word to be read is used to generate the parity again. The Syndrome Generator compares the newly generated parity with the read-out parity to produce the syndrome that contains the information for error bits. The Error Corrector corrects the error in the read-out data word if necessary, based on the Syndrome.

# D. Telecommand Processor

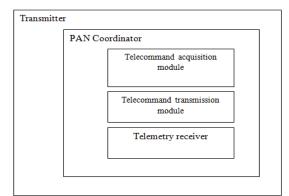

Figure 5: Block diagram of telecommand transmitter

In spacecraft application requirement, the star topology is selected, it is simple to implement and it has less complexity and it satisfies all the requirements of TC-TM systems. The PAN coordinator and FFD's are devices and they are configured as star topology.

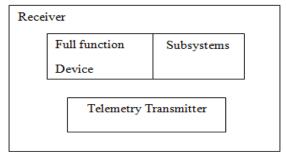

The PAN coordinator is interfaced with both TC and TM systems as shown in fig 5. The FFD's are interfaced with

other subsystems of the satellite as shown in fig 6. In PAN coordinator, received command from the EDAC unit and transfer to the Full Function Devices (FFD's) in subsystems and intended FFD receives command. It is decoded and converted as pulse or level or data command and it is executed in the subsystem end. Each FFD can execute any number of commands as required by the subsystems. In this fashion commands are distributed to subsystems through FFD's in wireless mode. The FFD's receives different heath parameters and payload data from respective subsystems and transmits to PAN coordinator.

Figure 6: Block diagram of Telecommand receiver

# IV. RESULTS AND DISCUSSIONS

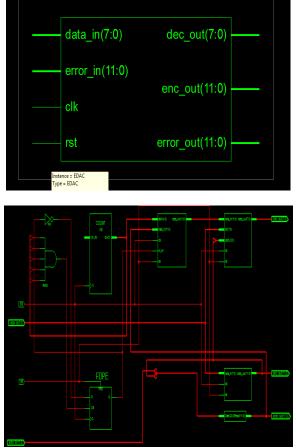

Results show the RTL schematic of EDAC unit, the simulation result of the RAM memory and transmitter section of telecommand system.

Figure 7: RTL Schematic of EDAC unit.

National Conference on Advanced Innovation in Engineering and Technology (NCAIET-2015)

## Alva's Institute of Engineering and Technology, Moodbidri

Figure 8: Simulation result of RAM memory.

Figure 9: Simulation result of telecommand transmitter.

Future works include its ASIC design and its [12] Recent Advances in Error/Erasure Correcting and Coding, Vijay implementation.

#### V. CONCLUSION

Consumer demands for high performance and rich driven the functionality have semiconductor [14] manufacturing industry to the integration of multiple complex components onto a single chip. As the complexity of the remotely located physical devices increases, the requirement for a greater telecommanding capability and efficiency arises, but present IP Core Based Architecture of telecommand System-on-a-Chip (SoC) has increased delay in transmission of data packets. By decreasing the delay system get better throughput and [17] L. Yin, J. Lu, K. Ben Letaief and Y. Wu, "Burst-error correcting increase its features. The new architecture is designed to analyze the scope for a performance enhancement with respect to the present system.

## REFERENCES

- [1] Rajesvari., Manoj G, Angelin Ponrani.M )"IP Core Based Architecture of Telecommand System-on-Chip (SoC) for Spacecraft applications "International Conference on Signal Processing, Image Processing and Pattern Recognition"-2013

- SoC: A Real Platform for IP Reuse, IP Infringement, and IP [2] Protection Debasri Saha and Susmita Sur-Kolay Advanced Computing and Microelectronics Unit, Indian Statistical Institute,

Kolkata 700108, India, Received 12 October 2010; Revised 4 January 2011; Accepted 24 January 2011

- Reduced Precision Redundancy for Satellite Telecommand [3] Receiver Module on FPGA Salman Sadruddin and Arshad Aziz, National University of Science and Technology (NUST), H-12, Islamabad, Pakistan, Hindawi Publishing Corporation ,Chinese Journal of Engineering, Volume 2013, Article ID 453872, 8 pages.

- The International Journal Of Engineering And Science (IJES) [4] Volume || 3 || Issue || 6 || Pages || 17-24 || 2014 || ISSN (e): 2319 -1813 ISSN (p): 2319 - 1805 www.theijes.com The IJES Page 17, FPGA Implementation of System-on-chip (SOC) Architecture for Spacecraft Application ,Kiran Kumar B.G ,Dr. Kaushik Bhattacharyya

- [5] International journal of electronics and communication engineering & technology(IJECET) ,Volume 5, Issue 8, August (2014), pp. 139-149, designing of telecommand system using system on chip(soc) for spacecraft control applications by Anupama sindgi, u.b.Mahadevaswamy

- Wireless Telecommand and Telemetry Systems for Satellite [6] Communication Using ZigBee Network" Ravichandran, P.N. Kulkarni S. Sharma, S. Vasudevamurthy, H.S. Vanitha, M. Lakshminarsimhan, P. Digital Syst. Group, ISRO Satellite Center, and Bangalore, India this paper appears in: Advances in Recent Technologies in Communication and Computing, 2009. ARTCom '09. International Conference.

- [7] System-on-Chip: Reuse and Integration Pre-designed and preverified hardware and software blocks can be combined on chips for many different applicationsVthey promise large productivity gains. By Resve Saleh, Fellow IEEE, SteveWilton, Senior Member IEEE, Shahriar Mirabbasi, Member IEEE.

- [8] X. Yu, J. Modestino, and I. Bajic, -Performance analysis of the efficacy of packet-level FEC in improving video transport over networks, I in Proc. IEEE Int. Conf. Image Process. (ICIP '05), pp. II-177-II-180.

- [9] Reed Solomon Forward Error Correction Codes. http://en.wikipedia.org/wiki/Reed-Solomon\_error\_correction

- [10] Dan Jurca et al, -Forward Error Correction for Multipath Media Streaming IEEE Transactions on circuits and systems for video technology, vol. 19, no. 9, pp 1315-1326, September 2009

- Why Digital Fountain's Raptor Code Is Better Than Reed Solomon [11] Erasure Codes For Streaming Applications, 2005 Digital Fountain, Inc.

- Subramanian. Networks Lab RPI. http://networks.ecse.rpi.edu/pubs/ecc.ppt

- [13] 3GPP TSG-SA4#31 Tdoc S4-040348 May 17-21, 2004, Montreal, Canada, Simulation Guidelines for the Evaluation of FEC Methods for MBMS Download and Streaming Services.

- Frenger, P., P. Orten, and T. Ottosson, "Convolution Codes with Optimum Distance Spectrum," IEEE Communications Letters, vol. 3, pp. 317-319, November 1999.

- Ufuk DEMIR and Ozlem AKTA\$ -Raptor versus Reed Solomon Forward Error Correction Codes| Proceedings of the Seventh IEEE International Symposium on Computer Networks (ISCN'06) pp 264-269, 2006

- [16] B. Fong et al. -Forward Error Correction with Reed-Solomon Codes for Wearable Computersl IEEE Transactions on Consumer Electronics, Vol. 49, No. 4, pp 917-921, NOVEMBER 2003

- algorithm for Reed-Solomon codes", Electronics Letters, Vol. 37 No. 11, May 25, 2001, pp. 695-697

- [18] Ted H. Szymanski, Optical Link Optimization Using Embedded Forward Error Correcting Codesl IEEE Journal of selected topics in quantum electronics, vol. 9, no. 2, pp 647-656, March/April 2003

- [19] Peter Klapproth, -General Architectural Concepts for IP Core Re-Use -Proceedings of the 15th International Conference on VLSI Design (VLSIDí02), 2002

- [20] Mr.Anjan.D, Mrs.Ashwini.s.shivannavar, Dr. M. Z. Processing, Kurian.National Conference on VLSI Signal Communication and Soft Computing (NCVCS-14) -2014