# FPGA Implementation of FIR Filter Using Bit Serial Arithmetic Technique

## Mr. Shridhar Devamane

Assistant Professor, Department of Electronics & Tele-communication Engineering, Nagesh Karajagi Orchid College of

## Engineering & Technology, Solapur, Maharashtra, India

Abstract: Implementing hardware design in Field Programmable Gate Arrays (FPGAs) is a formidable task. There is more than one way to implement the dsp design for digital FIR filter. The traditional approach is based on application of general purpose multipliers. However, multipliers implemented in FPGA architectures do not allow constructing economic Digital Filters. For this reason, multipliers are replaced by Lookup Tables and Adder Subs tractor, which use Bit-Serial Arithmetic.

Keywords: Digital filter, FIR filter, Look up table

#### **INTRODUCTION** I.

which performs numerical calculations on sampled multiplication operations, which are expensive in terms values of the signal. The analog input signal must first of time and space. Therefore, several techniques are used be sampled and digitized using an Analog to Digital to minimize the hard- ware needed to implement a filter. Converter (ADC). The resulting binary numbers, A technique widely used is to replace Bit-Parallel by representing successive sampled values of the input Bit-Serial structures. signal, are transferred to the filter, which carries out numerical calculations on them. These calculations typically involve multiplying the input values by constants and adding the products together. If necessary, the results of these calculations which now represent sampled values of the filtered signal, are output through a Digital to through the same logic, in a huge reduction in the Analog Converter (DAC) to convert the signal back to required analog form. In the last years digital filters have been approach 1/n of the hardware required for the n-bit recognized as primary digital signal processing (DSP) parallel design. The price of the logic reduction is that operation.

There are two basic types of digital filters, Finite Impulse Response (FIR) and Infinite Impulse Response (IIR) filters. FIR and IIR filters are used in many digital signal processing systems to per- form a variety of signal filtering and conditioning functions. An IIR filter is capable of emulating the transfer functions of analog continuous-time filters, such as low-pass, band-pass, An Approach to overcome the drawback of using high-pass, and all- pass (phase-shifting) types of filtering general purpose multiplier used in the FIR filter IIR filters exhibit similar phase characteristics as their analog counterparts. For arbitrary transfer functions makes use of bit serial arithmetic technique to with linear-phase response, FIR filters are utilized and design economic filters. have no equivalent in the analog domain.

On the other hand. the advances in Field Programmable Gate Arrays (FPGA) technology have This paper is organized as follows enabled these devices to be applied to a variety of • applications traditionally reserved for Application Specific Integrated Circuits (ASICs). The advantages of the FPGA approach to digital filter implementation include: higher samples rates than those that are available from traditional DSP chips lower costs than A. an ASIC for Moderate volume applications, and are more flexible than the alternate approaches.

A Digital Filter is a Linear Time Invariant (LTI) system A filtering function is usually carried out by a number of

Bit-Parallel structures process all the bits of input data simultaneously at a significant hardware cost. Bit-Serial, by comparison, process the input one bit at a time The advantage of the last one is that all the bits pass hardware. Typically, the Bit-Serial serial hardware takes n clock cycles to execute in one clock cycle. Since for certain classes of applications, FPGA utilization is high, performance goals are achieved while using economically attractive FPGA devices. For applications that require high speed performance, Bit-Parallel structures yield the highest performance.

#### **PROBLEM STATEMENT** II.

design. An efficient design methodology which

#### III. **PROPOSED WORK**

- The bit Serial arithmetic technique

- Structure of FIR Filter

- Experimental results

#### IV. METHODOLOGY

## Bit Serial Arithmetic Technique

Bit parallel designs process all of the bits of an input simultaneously at a significant hardware cost. In contrast, a bit serial structure processes the input one bit at a time,

INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 2, Issue 10, October 2014

generally using the results of the operations on the first bits to influence the processing of subsequent bits. The advantage enjoyed by the bit serial design is that all of the bits pass through the same logic, resulting in a huge reduction in the required hardware. Typically, the bit serial approach requires  $1/n^{th}$  of the hardware required for the equivalent n-bit parallel design. The price of this logic reduction is that the serial hardware takes n clock cycles to execute, while the equivalent parallel structure executes in one. The time-hardware product, however, for the serial structure is often smaller than for equivalent parallel designs because the logic delays between registers are generally significantly smaller. This means that the serial machine can operate at a higher Clock frequency In the case of FPGAs; signal routing contributes significant propagation delays and often uses up logic cells.

The serial structures tend to have very localized routing, often to only one destination. In contrast, the parallel machines usually need signals extended across the width of the processing element. The limited and slow routing resources in FPGAs make the serial processing elements even more attractive. In some cases, the overall throughput for a serial design implemented in an FPGA can actually exceed of an equivalent parallel design in the same device.

## B. FIR Filter Design

In a FIR-Digital Filter the output depends only of present and previous input samples, which are multiplied by a set of coefficients and then added together to produce the output. The filter behaviour is determined by the filter coefficients. A general FIR-filter is characterized by the following equation

$$y^{n} = a_{0}x^{n} + a_{1}x^{n-1} + \dots + a_{q}x^{n-p}$$

where p is the filter order, the  $a_p$  are the filter coefficients,

$x^n$  is the input signal at the time step n, and  $y^n$  is the output signal at the step n.

The major disadvantage of these filters is that usually a large number of coefficients are required to control adequately their frequency response. Practical FIR-Filters typically need between 10 and 150 coefficients.

This makes them slower in operation than most IIR-filter design. Expanding the above equation

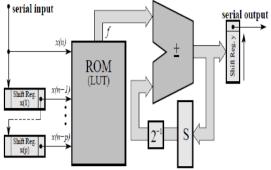

$y^n = \sum 2^j f(x_{j}^n, x^{n-1}, ..., x^{n-p}) - f(x_0^n, x^{n-1}_0, ..., x^{n-p}_0)$ Fig below shows the architecture to compute the filter equation

Fig. 1: FIR Filter Using Bit Serial Arithmetic

As we know FIR filters have no feedback coefficients. Due to this, a After l+1 cycles, the adder-Subtracter output is only stored into y(n) register.

# C. Experimental Results

The filter implementation consist of 8 bit input samples and there coefficients have 12 bit precision. The FPGA selected was Spartan 3AN kit.

Table.1: Design Summary of FIR filter bit serial arithmetic technique

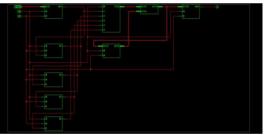

Fig. 2: RTL Diagram of FIR Filter Architecture

Fig.3: Simulation Waveform of 8 Bit FIR filter Architecture

# V. CONCLUSION

The presented paper results allows us to construct the higher order economic FIR filters and using interconnection techniques without the of use huge look up tables. The result produced by these techniques can be straight forward translated from their schematic representation into VERILOG code and then synthesize it on an FPGA SPARTAN 3AN.

INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 2, Issue 10, October 2014

## ACKNOWLEDGMENT

Authors would like to thank the Department of Electronics and Tele-Communication Engineering and also those individuals who have motivated and helped in carrying this work successfully.

#### REFERENCES

- [1] Monica Arraoyuelo, Jorge Arroyuelo, Alejanadro Grosso." FPGA-Based Digital Filters using bit serial arithmetic", University Nacional de San Luis, Republica argentina. arithmetic", university Nacional de San Luis, Republica argentina.

- [2] Kunt Arne Vinger and Jim Torrensen, "Implementing Filters", EUSIPCO 2005- 13 The European Signal Processing Conference. Antalya, Turkey. September 4-8, 2005.

- [3] Kalivas, Tsirikos, Bougas and Pekmestzi, "100% Operational Efficient Bit-Serial Programmable FIR Digital Filters", EUSIPCO 2005-13 The European Signal Processing Conference. Antalya, Turkey. September 4-8, 2005.

- [4] Chi-Jui Chou, Satish Mohanakrishnan and Joseph Evans, "FPGA Implementation of Digital Filters", International Conference on Signal Processing Application and Technology. Berlin, 1993. Pages 251-255.

- [5] Sang-Hun Yoon, Jong Wha Chong and Chi-Ho Lin", An Area Optimization Method for Digital Filter Design". ETRI Journal, volume 26, Number 6. December 2004, Pages 545-553.

- [6] Rawski, Tomaszewicz, Selvaraj and Luba. "Efficient Implementation of Digital Filters with use of Advanced Synthesis Methods Targeted FPGA Architectures", Digital Evolution of FIR-Filters Efficiently in an FPGA", Evolvable Hardware, Proceedings, NASA/DoD Conference on July 9-11, 2003. Page 26-29.

#### BIOGRAPHY

**Mr. Shridhar B Devamane** is working as Assistant Professor in Electronics and Telecommunication Department at N K Orchid College of Engineering and Technology, Solapur. He has four year

teaching experience. He has obtained B. E. Degree in Electronics and Communication and M. Tech. in VLSI Design & Embedded System. His area of interest are VLSI Design and Embedded system and Low power VLSI Design.